Primary Ref: AD9361 Reference Manual

Some notes on research I was doing on the AD9361.

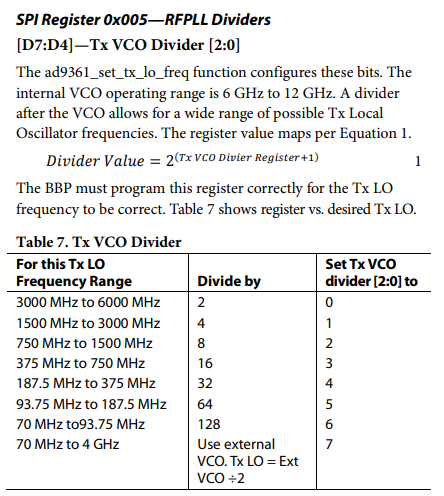

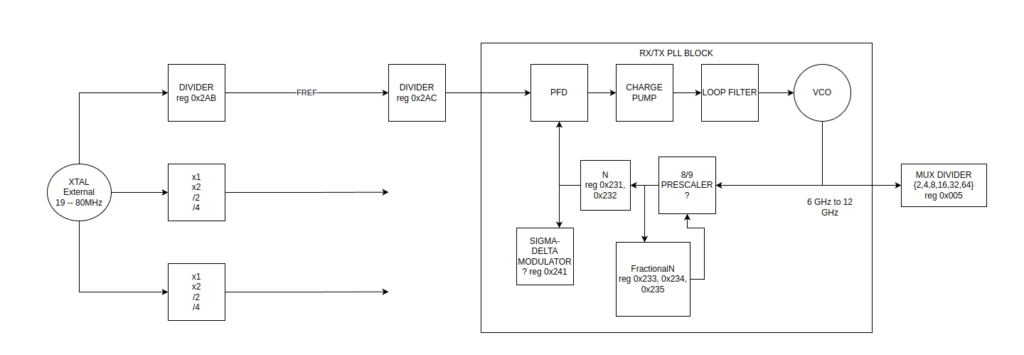

The Main PLL block generates a frequency, locked to the external clock reference, from 6 GHz to 12 GHz. This then goes to a divider chain.

The result of the divider chain is an I/Q clock that becomes the output center frequency.

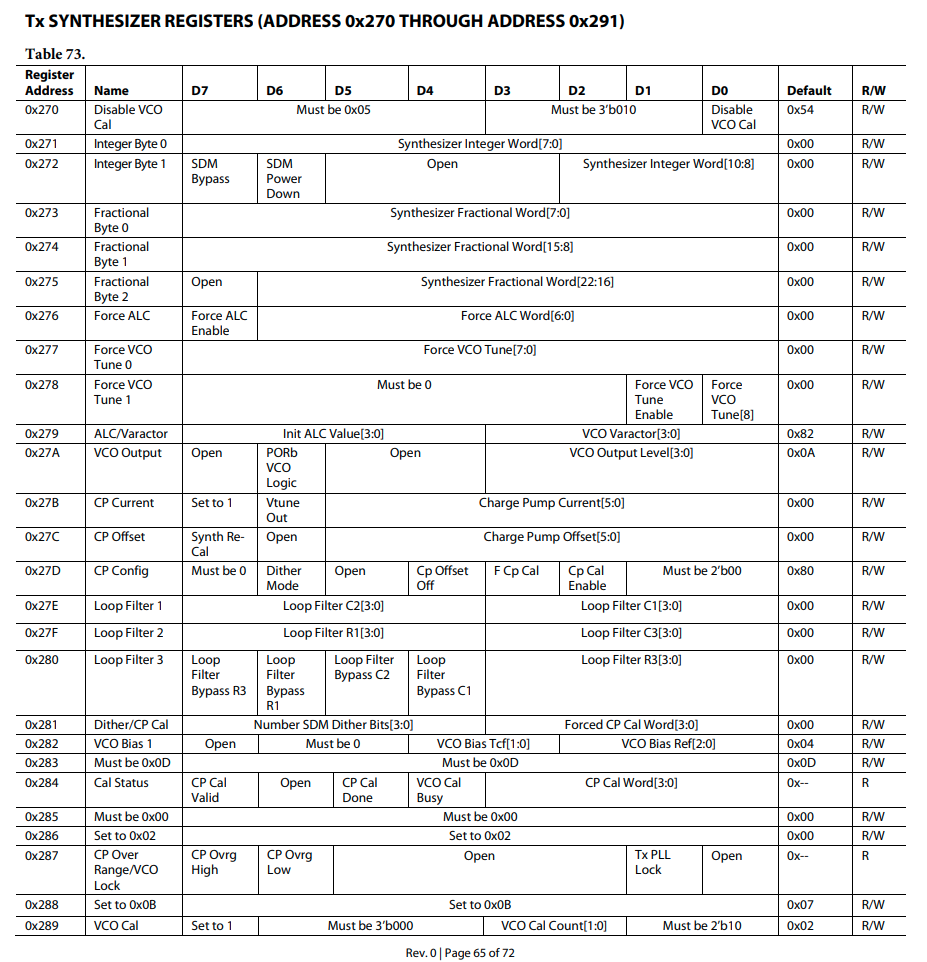

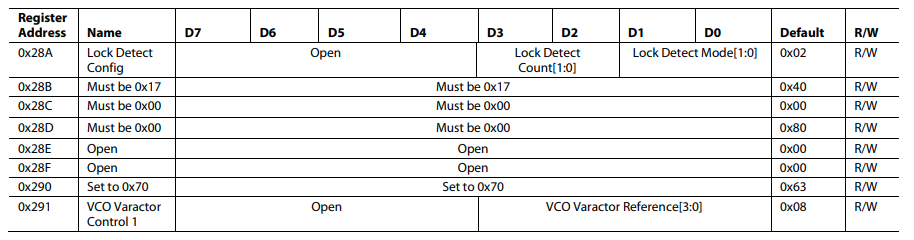

The synthesizer is configured by registers 0x270 through 0x290

The code

The AD9361 frequencies/clocks/PLLs are configured using the (no-os) function: